# Design of ESD protections for ECG applications

Pablo Jesús Gardella Buenos Aires Institute of Techonology (ITBA) Buenos Aires, Argentina pgardell@itba.edu.ar Eduardo Baez

Buenos Aires Institute of Techonology

(ITBA)

Buenos Aires, Argentina

ebaez@itba.edu.ar

Juan Manuel Cesaretti

Buenos Aires Institute of Techonology

(ITBA)

Buenos Aires, Argentina

jcesaret@itba.edu.ar

Abstract—This paper presents the design of Electrostatic Discharge (ESD) protections for a remote Electroencephalograph (ECG). Design and layout guidelines are analyzed to improve the ESD robustness of a Grounded-Gate NMOS (GGNMOS) cell based on a single well CMOS-only process. Experimental validation is done by means of a Time Domain Reflectometry (TDR) technique known as Transmission Line Pulse (TLP) testing. The silicon implementation of the proposed design passes ±3700V in the Human-Body Model (HBM).

Keywords— Electroencephalography (ECG), Electrostatic discharge (ESD), Human-Body Model (HBM), Transmission Line Pulse (TLP), Time Domain Reflectometry (TDR)

#### I. Introduction

The Electrostatic Discharge (ESD) robustness of electronic systems is of utmost importance in the design of any kind of electronic systems. This is particularly true for biomedical systems such Electrocardiographs (ECG), Electroencephalograms (EEG), Oximeters, implantable devices and every single device where the life of a patient is at risk [1], [2], [3], [4] and [5]. Since electrical safety regulations do not allow grounding the patients (to drain out the electrostatic charges that may get accumulated on their skin), preventive measures to avoid these charges from damaging the electronic circuitry shall be addressed. In this regard, the Human-Body Model (HBM) standard considers the ESD strikes of human beings as double exponential waves whose rise time is in the order of 1-10ns and its fall time in the range of 100-200ns. These characteristics are very well mimicked by ESD testers, whose inner cores are nothing more than RC networks where the capacitance determines the energy of the discharge and the resistance, the decay.

Few of the educationally available Multi-Project Wafer (MPW) platforms provide basic libraries to deal with ESD events, while most lack information about it. This is the case despite the huge importance of this area in terms of safety and reliability. Moreover, limited works can be found on the bibliography concerning the low-level design of ESD structures. Consequently, this work proposes to tackle such shortage.

In [6], a cascade of 3 Grounded-Gate NMOS (GGNMOS) structures is presented as the protection mechanism for ESD hazards, with some additional RC filtering. However, neither design, layout guidelines nor measurements are presented.

Moreover, the input impedance of this approach is being compromised by the filters and it won't allow to apply a chopper-stabilized topology as the ones presented in [7], [8] and [9] which will be the targeted application of this work.

In [10], a Silicon-Controlled Rectifier (SCR) on a 0.18µm CMOS process is presented with measurements that validate the performance. However, neither design nor layout guidelines are presented.

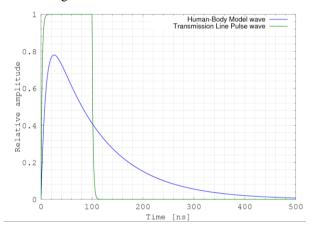

One of the main challenges in ESD design is the validation of the structures. Not only because ESD testers are rather expensive but also because the testing procedure with such equipment is self-contained. This means that ESD testers do not provide more information than a Pass / Do not pass result, making the design and debugging process quite challenging. In order to overcome with this limitation, a Time Domain Reflectometry (TDR) technique called Transmission Line Pulse (TLP) testing was used. The benefits of this approach rely not only on a cost perspective but also on the fact that it is an inherently more insightful approach that gives a better understanding of how the structures work and how do they dynamically behave against the ESD event [11]. Fig. 1 shows a theoretical comparison of both waveforms for a given amount of electrical charge.

Fig. 1. Double exponential HBM wave and TLP wave.

This paper is organized as follows: Section II describes the design procedure of the ESD protections with some guidelines in terms of layout. Section III presents the TLP technique and its correlation with the HBM standard. Afterwards, the experimental results are presented in Section IV and finally, in Section V the conclusions of this paper are drawn.

## II. DESIGN

ESD is a particular case of a charge-driven event, where their movement leads to high current densities and subsequently high voltages, which result in high electric fields. Consequently, the failure modes can be either from a thermal or an electric source. In the former, Joule effect heats up the structures, while on the latter the high electric field causes charge injection or dielectric breakdown. These failures are highly dependent on the manufacturing technology, for example processes with insulated substrate such as Silicon On Insulator (SOI) and Silicon On Sapphire (SOS) have a larger thermal mass that prevents the heat from being removed as effectively as in a LOCal Oxidation of Silicon (LOCOS) process, where the energy of the ESD strike can be absorbed much more conveniently since there is no insulator acting as an electrical (and thermal) barrier [12]. On the other hand, in LOCOS processes, the interface between thick and thin oxides are usually a weak point from an electric field perspective and although this can be improved with Lightly Doped Drain (LDD) implants, it comes with larger power dissipation as it will be described afterwards.

The goal of every ESD protection is as simple as to clamp the voltage to a safe level and to provide a safe path for the high current while withstanding the energy delivered by the external source. Note that these protections are meant for handling energy events rather than power events. In fact, since the onresistance of ESD protections is more than 2 orders of magnitude below the HBM network resistance, the ESD event can be thought as a finite-energy current source.

There are out-die and in-die protections, in the case of the former, these protections include Transient Voltage Suppressors (TVS), Gas Discharge Tubes (GDT), Metal-Oxide Varistor (MOV) or even the discrete version of in-die protections. However, the main drawback of all these devices is that they do not protect the DUT until they are properly interconnected. It leaves the front-end circuitry vulnerable during the product assembly which, in general, is one of the most critical stages in terms of ESD hazards. The most common approaches among in-die protections are simple diodes (including Zeners or even mere rectifiers), Grounded-Gate-NMOS (GGNMOS) and Silicon Controlled Rectifiers (SCR). In the case of the last two, the main drawback is the risk of having false triggering, which can cause device destruction if it happens during nominal operation.

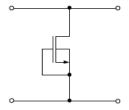

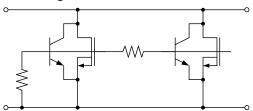

In this work, GGNMOS structures [12], [13], [14] will be used as in [6] and [10]. In these devices, the lateral parasitic NPN buried within an NMOS is used to handle the ESD current. A schematic view of the device is shown on Fig. 2.

Fig. 2. Schematic of a GGNMOS protection.

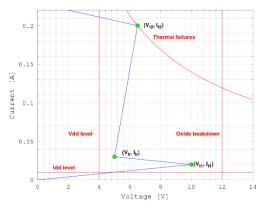

With the gate grounded, the drain voltage can raise until the drain-body junction enters in avalanche breakdown ( $V_{tl}$ ,  $I_{tl}$ ), which should be lower than the gate oxide breakdown. At this point, current develops a voltage drop to forward bias the body-source junction injecting more electrons into the base region. After this, an snapback ocurrs and the drain voltage drops significantly as a result of the enhanced conductance of the NPN path ( $V_h$ ,  $I_h$ ). These values are known as holding or sustaining because going below them will turn off the bipolar. Therefore, in the design of GGNMOS structures, it is crucial that the power supply voltage ( $V_{dd}$ ) and the supply current ( $I_{dd}$ ) are below  $V_h$  and  $I_h$  respectively as shown on Fig. 3. Otherwise, several GGNMOS can be stacked to meet the voltage requirement.

Fig. 3. GGNMOS typical I-V curve and its SOA.

On the other hand, the second or thermal breakdown point ( $V_{t2}$ ) is also known as the limit of the Safety Operating Area (SOA), because stressing the device beyond it will cause a physical non-reversible change on its inner structure. Moreover, this point shall be larger than  $V_{t1}$  when multiple structures are parallelized, otherwise the branches could get destroyed one by one before the others even turn on.

Several technology parameters have to be taken into account when designing these kind of structures. For example, the thickness of the wafer (in single-well processes) or the epitaxial layer will affect the performance not only from a heat flow perspective, where the SOI and LOCOS processes are the extreme cases, but also from an electrical perspective. Because the amount of current required to trigger the parasitic NPN (at  $V_{tl}$ ) will be inversely proportional to the intrinsic resistance of the well, which is defined by its physical dimensions and doping profile.

In adittion to that, LDD implants have been widely used by the industry to improve hot carrier performance since it reduces the electric field at the oxide surface preventing carriers to get stuck on it and shifting the transistor threshold as a consequence. However, the lower doping of these regions comes with a larger resistance in the channel that produces a higher  $V_h$  and more heat dissipation for a given amount of current.

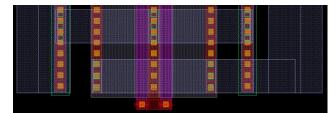

On the other hand, non-uniform current densities across the multiple fingers of a GGNMOS structure is not suggested. In this scenario, an extended drain geometry as the one presented on Fig. 4 is required to ballast the current densities. The increased resistance of this extended N+ regions guarantees a uniform current distribution among parallel GGNMOS [13]. However, low-resistance silicide can still lead to non-uniform current distribution. Therefore a blocking layer over the drain extension region is mandatory in order to force the current to flow through the n-well diffusion instead of over the silicide. This avoids not only current crowding but also current filamentation [13]. The main drawback of this approach is the obvious need of an extra mask. However, in [15] some layout techniques to avoid it are discussed for Fully-Silicided processes.

Fig. 4. Layout view of two fingers of a GGNMOS structure.

Fig. 5 shows the substrate resistance of GGNMOS structures. In the case of parallel structures, special attention should be paid to guarantee the minimum body-source resistance from one finger to the subsequent, as well as systematic increases from one structure to the next one. In terms of substrate contacts, since they provide an undesired current path for the body current, it is recommended to exclusively have them in the structure surroundings.

Fig. 5. Parasitic devices of the GGNMOS cells.

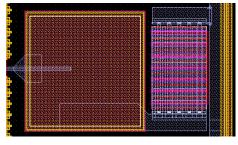

The protections must be placed as close as possible to the bond pads. Therefore, a GGNMOS clamp (as the one shown in Fig. 2) was implemented for every pin. The structures have been sized with a W/L= $50\mu$ m/1 $\mu$ m to provide a compact layout in combination with the pads as shown in Fig. 6.

Fig. 6. Layout view of a ESD cells.

#### III. CHARACTERIZATION BENCH

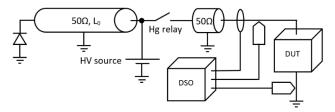

The Transmission Line Pulse (TLP) testing approach is a well-known technique for studying ESD protections [11]. The concept behind this Time Domain Reflectometry (TDR) technique is that the discharge pulse mimics, in terms of energy, an HBM pulse. The following picture shows the standard setup of a constant impedance TLP bench [16], where the most critical component is the fast mercury (Hg) relay that needs to guarantee a debounced contact in order to effectively deliver the ESD strike to the load. The relation between the TLP rating and the HBM equivalent rating is a factor of  $1500\Omega$  [11].

Fig. 7. Constant impedance (50 $\Omega$ ) TLP bench.

Pulse width turns out to be the time it takes to discharge the precharged transmission line of length  $L_0$  by a travelling wave of propagation velocity v calculated in (1)

$$v \cong \frac{c_0}{\sqrt{\varepsilon_r}} \tag{1}$$

Where  $c_0$  is the speed of light in vacuum and  $\varepsilon_r$  is the relative dielectric constant of the transmission line insulator, which for an RG-316 cable is 2.25. Therefore, for a 100ns pulse (as required to meet the HBM model [11]), 10m of cable are needed.

Several works have proved a miscorrelation between HBM and TLP results when the triggering mechanism of the protections is susceptible to the high dv/dt content of the ESD pulse [11]. To test a worst-case scenario, this works uses a rise time of 1ns and a pulse width of 100ns.

## IV. EXPERIMENTAL RESULTS

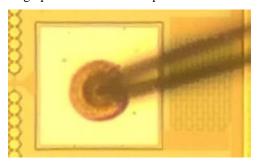

The GGNMOS structures have been implemented on a  $0.5\mu m$  CMOS-only process by a Multi-project Wafer (MPW) Fabrication Service provided by MOSIS. Fig. 8 provides a microphotograph of the GGNMOS protection.

Fig. 8. Die microphotograph of the ESD structure in Fig. 6.

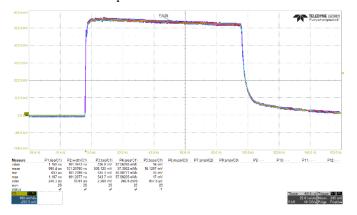

The following measurement has been logged with a LeCroy HD09104 at 4Gsa/s and shows the TLP pulse over a  $50\Omega$  load, where no reflection took place. Note the rise time 10% to 90%

is 0.990ns±0.267ns and the pulse width is 101.267ns±0.058ns over a set of 25 samples.

Fig. 9. TLP pulse measurement over a  $50\Omega$  load.

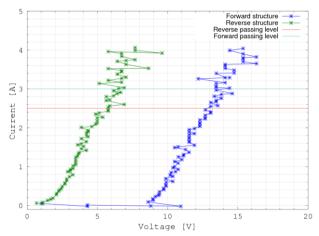

The I-V results of the TLP tests are shown in the following figure.

Fig. 10. Forward and reverse TLP I-V plot of the GGNMOS.

In the I-V curves it is seen that the reverse protection is achieving a 2.5A level while the forward is achieving 3.0A, which correspond to -3700V and +4500V, respectively, in the HBM standard  $(1.5k\Omega, 100pF)$ . Leakage current was the criteria to determine the failure mode.

Other standards such as the International Electrotechnical Committee (IEC) 61000-4-2 standard have not been tested due to the requirement of an ESD tester.

#### V. CONCLUSIONS

The design of ESD protection structures for biomedical applications have been presented including both design and layout guidelines. The performance has been successfully characterized based on a cost-effective TDR approach that guarantees the structures are reaching at least  $\pm 3700 \text{V}$  in the Human-Body Model.

### REFERENCES

- [1] T. Viheriäkoski, M. Kokkonen, P. Tamminen, E. Kärjä, J. Hillberg and J. Smallwood, "Electrostatic threats in hospital environment," *Electrical Overstress/Electrostatic Discharge Symposium Proceedings* 2014, Tucson, AZ, 2014, pp. 1-9.

- [2] J. Liu et al., "ESD protection and biomedical integrated circuit co-design techniques," 2011 IEEE Biomedical Circuits and Systems Conference (BioCAS), San Diego, CA, 2011, pp. 405-408.

- [3] M. Kohani, A. Bhandare, L. Guan, D. Pommerenke and M. G. Pecht, "Evaluating characteristics of electrostatic discharge (ESD) events in wearable medical devices: comparison with the IEC 61000-4-2 standard," in *IEEE Transactions on Electromagnetic Compatibility*, vol. 60, no. 5, pp. 1304-1312, Oct. 2018.

- [4] J. Zhou et al., "An ESD demonstrator system for evaluating the ESD risks of wearable devices," 2017 39th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Tucson, AZ, 2017, pp. 1-7.

- [5] T. Ishida, S. Nitta, F. Xiao, Y. Kami and O. Fujiwara, "An experimental study of electrostatic discharge immunity testing for wearable devices," 2015 IEEE International Symposium on Electromagnetic Compatibility (EMC), Dresden, 2015, pp. 839-842.

- [6] M. Barsaiyan and P. P. Bansod, "Protection circuit design for Electrocardiograph (ECG) with input filtering," 2017 8th International Conference on Computing, Communication and Networking Technologies (ICCCNT), Delhi, 2017, pp. 1-4.

- [7] J. Wu, M. Law, P. Mak and R. P. Martins, "A 2-µW 45-nV/√Hz readout front end with multiple-chopping active-high-pass ripple reduction loop and pseudofeedback DC servo loop," in *IEEE Transactions on Circuits* and Systems II: Express Briefs, vol. 63, no. 4, pp. 351-355, April 2016.

- [8] P. J. Gardella, E. Villa Fernandez, E. Baez and J. M. Cesaretti, "A chopped front-end system with common-mode feedback for real time ECG applications," 2017 IEEE 8th Latin American Symposium on Circuits & Systems (LASCAS), Bariloche, 2017, pp. 1-4.

- [9] P. J. Gardella, E. Villa Fernandez, E. Baez, N. Biberidies and J. M. Cesaretti, "Low noise front-end and ADC for real-time ECG system in CMOS process," 2019 IEEE 10th Latin American Symposium on Circuits & Systems (LASCAS), Armenia, Colombia, 2019, pp. 1-4.

- [10] C. Lin and Y. Chiu, "High-voltage driving circuit with on-chip ESD protection in CMOS technology," 2017 International Conference on Intelligent Informatics and Biomedical Sciences (ICIIBMS), Okinawa, 2017, pp. 223-224.

- [11] J. Barth, K. Verhaege, L. G. Henry and J. Richner, "TLP calibration, correlation, standards, and new techniques [ESD test]," *Electrical Overstress/Electrostatic Discharge Symposium Proceedings 2000 (IEEE Cat. No.00TH8476)*, Anaheim, CA, USA, 2000, pp. 85-96.

- [12] J. E. Vinson and J. J. Liou, "Electrostatic discharge in semiconductor devices: protection techniques," in *Proceedings of the IEEE*, vol. 88, no. 12, pp. 1878-1902, Dec. 2000.

- [13] Dabral, S., & Maloney, T. J. (1998). Basic ESD and I/O design. New York: John Wiley & Sons, pp. 22-25.

- [14] J. Shi, "ESD characteristics of GGNMOS device in deep sub-micron CMOS technology," 2016 International Conference on Audio, Language and Image Processing (ICALIP), Shanghai, 2016, pp. 327-331.

- [15] M. Ker, W. Chen, W. Shieh and I. Wei, "Electrostatic discharge protection design for high-voltage programming pin in fully-silicided CMOS ICs," in *IEEE Journal of Solid-State Circuits*, vol. 46, no. 2, pp. 537-545, Feb. 2011.

- [16] E. Grund and R. Gauthier, "TLP systems with combined 50Ω and 500Ω impedance probes and Kelvin probes," in *IEEE Transactions on Electronics Packaging Manufacturing*, vol. 28, no. 3, pp. 213-223, July 2005