# Voltage-Driven Hysteresis Model for Resistive Switching: SPICE Modeling and Circuit Applications

German Agustin Patterson<sup>©</sup>, J. Suñé, Fellow, IEEE, and E. Miranda, Senior Member, IEEE

Abstract—Resistive switching devices are nonlinear electrical components that have drawn great attention in the design of new technologies including memory devices and neuromorphic circuits. In this paper, an SPICE implementation of a novel compact model is presented and put under test by means of different circuit configurations. The model is based on two identical opposite-biased diodes in series with a resistor where the switching behavior is governed by the creation and rupture of multiple conductive channels. Results show that the model is stable under different input sources and amplitudes and, with special interest, in multielement circuits. The model is validated with experimental data available in the literature. Both the corresponding SPICE code and schematic are provided in order to facilitate the model use and assessment.

Index Terms—Memristor, resistive switching, SPICE.

## I. INTRODUCTION

EMRISTIVE elements are two-terminal devices that present variable resistance [1]. The change of the resistance depends on the history of the device, i.e., it has a hysteretic relationship between the applied electric field and the current through. By combining these elements, there is a huge variety of potential applications where memristive devices can be used such as memory devices, neuromorphic systems, analog and chaotic circuits, and computational logic, among others [2]–[6].

Numerical simulations are of great benefit when designing and characterizing circuits involving memristive elements. For such, a simple and accurate model that embodies the major fingerprints observed in experiments is needed to be developed. Many SPICE models reported in the literature are commonly associated with the first memristor definition

This work was supported in part by the PANACHE Project through the Spanish Ministerio de Economía y Competitividad-EU FEDER Program and ENIAC Joint Undertaking under Grant PCIN2013-076 and Grant TEC2012-32305, and in part by the DURSI through the Generalitat de Catalunya under Grant 2014SGR384. This paper was recommended by Associate Editor S. K. Lim.(Corresponding author: German Agustin Patterson.)

G. A. Patterson is with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain and also with the Departamento de Informática, Instituto Tecnológico de Buenos Aires, Buenos Aires 1437, Argentina (e-mail: gpatters@itba.edu.ar).

J. Suñé and E. Miranda are with the Departament d'Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Bellaterra, Spain.

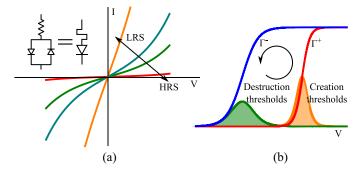

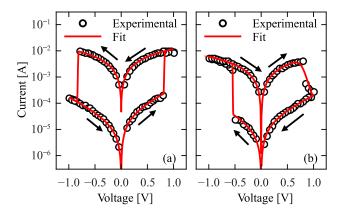

Fig. 1. (a) Model schematics and characteristic curve. The model consist of two opposite-biased diodes in series with a resistor. Parameter variations modify the conduction curve. (b) Thresholds distributions of creation and destruction of channels follow approximately bell-shaped distributions. The function  $\Gamma^\pm$  describes the number of activated channels as a function of the applied voltage. The arrow indicates the direction of the cycle.

put forward by Strukov et al. [7], Batas and Fiedler [8], Rak and Cserey [9], and Biolek et al. [10]. Although, these models do not account for many of the features observed in experiments, e.g., threshold-type switching [11]. Recently, a novel compact model that takes into account voltagedependent hysteresis, and that is able to describe the major and minor current-voltage loops in bipolar resistive switches, was reported in [12] and [13] and experimentally validated in [14] and [15]. This model presents a characteristic curve that has a closed-form expression which is continuous and differentiable. In particular, the model is based on two identical opposite-biased diodes in series with a resistor as shown in Fig. 1(a). The I-V relationship resembles a diode with memory so that this device was termed memdiode. The switching behavior is related to the creation and rupture of multiple conductive channels in terms of a voltage-driven logistic hysteron [16]. Here, the SPICE implementation of the memdiode model is reported and the behavior of different circuit configurations is investigated. The original model is modified in order to be able to describe the temporal response of such as devices.

This paper is organized as follows. In Section II the basic features of the memdiode model are described while the SPICE modeling is introduced in Section III. Results are presented in Section IV where the influence of parameters is reported, parallel and series configurations are discussed. In this section, experimental results extracted from the literature are contrasted with the model proposed as also applications to 1R1S structures are shown. Finally, conclusions are drawn in Section V.

#### II. MODEL DESCRIPTION

The memdiode model consists of a transport equation that, under the appropriate model parameters, switches between a high resistive state (HRS) and a low resistive state (LRS) as depicted in Fig. 1(a). The underlying physical mechanism is governed by multiple conduction channels across the sample, where the set and reset voltages of the individual channels are assumed to follow a bell-shaped distribution [Fig. 1(b)], in particular, a logistic distribution. This is not a fundamental requirement and also other distributions can be used. The transport equation of the memdiode can be found from two identical opposite-biased diodes in series with a resistor. An approximate solution for this system, neglecting the inverse saturation currents, is given by [17]

$$I = \operatorname{sign}(V)I_0 \left\{ \frac{W \left[\phi \exp\left(\alpha |V| + \phi\right)\right]}{\phi} - 1 \right\}$$

(1)

with  $\phi = \alpha R_s I_0$ , where  $I_0$  is the current amplitude factor,  $\alpha$  a parameter related to the specific physical conduction mechanism,  $R_s$  the series resistance, and W the Lambert function. In order to include the hysteretic behavior, the internal state  $\lambda$  is defined according to

$$\lambda(V_t) = \min \left\{ \Gamma^-(V_t), \max \left[ \lambda(V_{t-\Delta t}), \Gamma^+(V_t) \right] \right\}$$

(2)

where  $\lambda(V_{t-\Delta t})$  is the value of  $\lambda$  in the previous time step. The ridge functions  $\Gamma^{\pm}$  are the solution of the logistic equation. These represent the sequential aggregation (+) or dissolution (-) of conductive channels as a function of the applied potential as shown in Fig. 1(b). These sigmoid functions are given by

$$\Gamma^{\pm}(V) = \left\{ 1 + \exp\left[-\eta^{\pm} \left(V - V^{\pm}\right)\right] \right\}^{-1} \tag{3}$$

where  $\eta^{\pm}$  are the transition rates, and  $V^{\pm}$  the threshold potentials. The state of the system is described by the vector  $\Omega = (I_0, \alpha, R_s)$  which in turn is a linear function of  $\lambda$  defined as  $\Omega = \Omega^{\min} + \lambda(\Omega^{\max} - \Omega^{\min})$ , where  $\Omega^{\min} = (I_0^{\min}, \alpha^{\min}, R_s^{\min})$  and  $\Omega^{\max} = (I_0^{\max}, \alpha^{\max}, R_s^{\max})$  are the end points of the vector  $\Omega$ , minimum and maximum, respectively. As a consequence of (2), it should be noted that the internal state will remain fixed while the applied voltage  $V_t$  meets the relationship given by

$$\Gamma^+(V_t) < \lambda(V_{t-\Delta t}) < \Gamma^-(V_t).$$

(4)

This simplified approach allows modeling samples that present threshold resistive switching, where it is necessary to overcome a certain voltage level to switch the resistive state.

According to [18], the Lambert function can be computed following the Hermite-Padé approximation given by:

$$W(x) \approx \ln(1+x) \left( 1 - \frac{\ln[1 + \ln(1+x)]}{2 + \ln(1+x)} \right).$$

(5)

The model presented in [12] and [13] does not meet one of the fundamental criteria of real memristors, that is, the effect

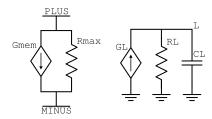

Fig. 2. Schematic of the SPICE compact model. The memdiode device consist of two current sources, two resistors, and a capacitor. The current source Gmem is driven by the voltage potential across PLUS-MINUS and the internal potential L. The latter is the voltage drop produced by the current source GL across CL.

that as the input frequency increases the hysteresis loop of the device becomes narrower. In order to include the aforementioned effect, a first-order differential equation is introduced to describe the evolution of the time-dependent internal-state variable  $\Lambda$ . This equation is defined as

$$\tau \frac{\mathrm{d}\Lambda}{\mathrm{d}t} + \Lambda = \lambda(V) \tag{6}$$

where  $\tau$  is the characteristic time involved in the transient response. Usually, the input voltage is a function of time, in this way, the general solution of (6) can be expressed as

$$\Lambda(t) = \exp\left(-\frac{t - t_0}{\tau}\right) \left\{ \int_{t_0}^t \frac{\lambda(V)}{\tau} \exp\left(\frac{s}{\tau}\right) ds + A \right\}$$

(7)

where A is a constant given by the initial condition  $\Lambda(t_0)$ , and the mute variable s is integrated between  $t_0$  and t. Within this framework, the vector  $\Omega$  is rewritten as a linear function of  $\Lambda$  according to

$$\Omega = \Omega^{\text{min}} + \Lambda \Big( \Omega^{\text{max}} - \Omega^{\text{min}} \Big). \tag{8}$$

Temperature effects are not included in this model because these are particularities of each type of device [19]–[23]. Nevertheless, they can be introduced in the model parameters in each particular situation.

# III. SPICE MODEL

The model presented in the previous section was implemented as an SPICE subcircuit. The circuit schematic is shown in Fig. 2. The two ports PLUS and MINUS represent the positive and negative terminals of the memdiode. The current source Gmem produces a current given by (1) taking into account the potential drop across PLUS and MINUS and the value of the internal state variable Λ which, in turn, is described by the potential across the capacitor CL. Resistor Rmax accounts for the nonideal behavior of the current source and it is necessary to overcome iteration problems and divide-by-zero errors when trying to combine more than one memdiode in an electric circuit. Note that, alternatively, it is also possible to invert (1) and design a subcircuit comprising a voltage source driven by the current through the device.

Equation (6) is implemented by means of a current source and a parallel RC circuit as shown in Fig. 2. The circuit cutoff frequency is given by the inverse of the characteristic time  $\tau = \text{RL }$  CL. The output of the current source GL is set equal to (2)

### TABLE I MEMDIODE SPICE MODEL CODE

```

* Memdiode SPICE model

.subckt memdiode PLUS MINUS L

** Block 1 - Model parameters **

* vp/vm: positive/negative threshold

np/nm: positive/negative transition rate

imax/imin: I0_max and I0_min

a: alpha parameter

Rs: series resistance

* LO: initial condition

RL: R_Lambda

* CL: C Lambda

Rm: R max

.params vp=2 np=100 vm=-1

nm=10 I.0=1e-10

imax=1e-2 a=3 Rs=1e2

imin=1e-6

+ RL=1 CL=1e-4 Rm=1e10

** Block 2 - Declare functions **

gp/gm: positive/negative ridge function

w: Lambert W function

I0: current amplitude factor

.func gp(V) \{1/(1+exp(-np*(V-vp)))\}

.func gm(V) \{1/(1+exp(-nm*(V-vm)))\}

.func w(x) \{ log(1+x) * (1-(log(1+log(1+x)))/(2+log(1+x))) \}

.func IO(L) {imax*L+imin*(1-L)}

** Block 3 - Current source - state variable **

GL 0 L value={min(gm(V(PLUS,MINUS)),

max(gp(V(PLUS,MINUS)),V(L)))/RL}

R L 0 {RL}

C L 0 {CL}

.ic V(L) = L0

** Block 4 - Current source - memristor **

Gmem PLUS MINUS value={sgn(V(PLUS, MINUS)) * (1/(a*Rs) *

w(a*R*10(V(L))*exp(a*(abs(V(PLUS,MINUS))+

Rs * I0(V(L))))-I0(V(L)))

Rmax PLUS MINUS {Rm}

.ends memdiode

```

divided by the value of RL. In this way, for input frequencies much lower than the cutoff frequency, the RC-output voltage follows the input-signal absolute magnitude.

The code of the subcircuit is presented in Table I. The code is separated in four main Blocks. Parameters involved in (1) and (3) are defined in the first Block as well as RL, CL, and Rmax. L0 is the initial condition of the state variable. Functions given by (2), (3), and (5) are declared in the second Block. Finally, Blocks 3 and 4 describe the circuits illustrated in Fig. 2 following (1), (2), and (6). Note that the value of  $\lambda(V_{t-\Delta t})$  in (2) is replaced by the actual value of L ( $\Lambda$ ). The state variable L0 ( $\Lambda_0$ ) is initialized in the third Block. The output L tracks the status of the internal state  $\Lambda$  during simulations and does not need to be connected.

For simplicity, this paper only considers variations of  $I_0$  [i.e.,  $I_0 = I_0(\Lambda)$ ], while  $R_s$  and  $\alpha$  remain as constants. However, variations of these are also allowed in the general model given by (8). All simulations were performed by setting  $RL = 1 \Omega$  and  $CL = 10^{-4}$  F unless otherwise stated. The code has been implemented in the free analog circuit simulator LTSPICE IV [24].

## IV. RESULTS

## A. Single Element

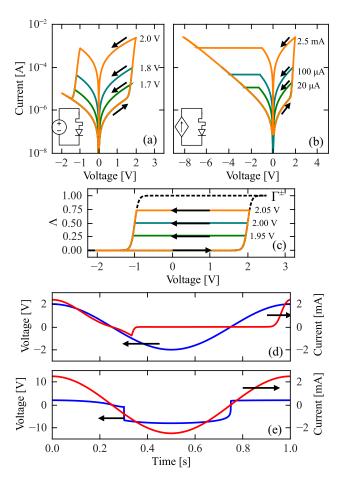

In this section, the model is tested under various input conditions. In Fig. 3 SPICE simulations are presented showing I-V characteristics and time evolutions when voltage and current sources are considered. Fig. 3(a) shows the I-V response of a single device driven by a voltage source. The applied

Fig. 3. SPICE simulations showing single memdiode I-V characteristics. Voltage (a) and current (b) driven memdiodes. The figure shows the response of the element for various input amplitudes. (c) Evolution of  $\Lambda$  for different voltage amplitudes. Dashed line accounts for the ridge functions  $\Gamma^{\pm}$ . Arrows indicate the direction of the cycles. (d) and (e) Typical time evolutions under both input sources. The parameters are:  $V^+ = 2$  V,  $V^- = -1$  V,  $\eta^+ = 20$  V $^{-1}$ ,  $\eta^- = 20$  V $^{-1}$ ,  $I_0^{\min} = 10^{-6}$  A,  $I_0^{\max} = 10^{-3}$  A,  $\alpha = 3$  V $^{-1}$ ,  $R_s = 100$   $\Omega$ , and Rmax  $= 10^{10}$   $\Omega$ .

waveform is sinusoidal with angular frequency  $\omega_0 = 2\pi$  rad/s. Three different amplitudes are considered where maximum amplitude values and spins are indicated in the figure. The model curves exhibit well-defined intermediate conductive states, that is, minor I-V loops arising from partial transitions of the state variable. Fig. 3(c) shows the evolution of the state variable  $\Lambda$  under different input signal amplitudes. Partial resistive transitions take place when the voltage is reversed midway. The time evolution of the voltage and current signals are shown in Fig. 3(d). Results taking into account a current source are also depicted in Fig. 3(b) and (e).

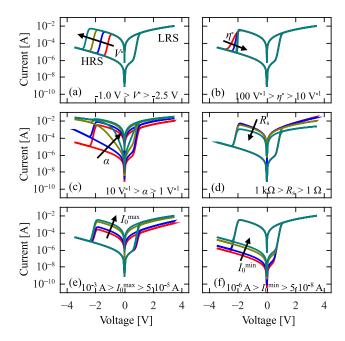

In order to have a better picture of the model overall behavior, Fig. 4 shows the influence of the model parameters on the current-voltage characteristic curves. The input signal is sinusoidal with amplitude 3.5 V and angular frequency  $\omega_0 = 2\pi$  rad/s. As it can be seen in Fig. 4(a) the threshold voltages determine the value at which the transitions occur. The rate of these transitions are given by  $\eta^{\pm}$  as shown in Fig. 4(b). The parameter  $\alpha$ , which is related to the physical conduction mechanism assumed (Schottky, tunneling, quantum point-contact, etc.), tunes the nonlinear response of the device

Fig. 4. Influence of parameters on the I-V characteristic curves. (a) and (b) Influence of the threshold potential and the transition rate, respectively. (c) and (d) Effect of  $\alpha$  and  $R_s$ . (e) and (f) Impact of the maximum and minimum current amplitude factor. Arrows indicate the direction of growth of the parameter. The model parameters are the same as those in Fig. 3 except:  $V^+ = 1 \text{ V}$  and  $V^- = -2 \text{ V}$ .

[see Fig. 4(c)]. The series resistor  $R_s$  provides a minimum resistance value further influencing the LRS as depicted in Fig. 4(d). Fig. 4(e) and (f) shows how  $I_0^{\text{max}}$  and  $I_0^{\text{min}}$  modulate the high- and low-conductive states.

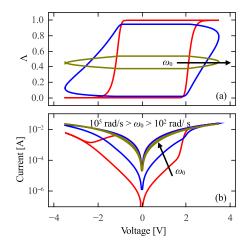

#### B. Dynamic Behavior

The dynamic behavior of the model was also analyzed. For that aim, a sinusoidal signal of amplitude 3.5 V was considered. Fig. 5 shows the response of the internal state  $\Lambda$  and current as a function of the input signal. Equation (6) imposes a response time for the evolution of the internal state. As can be seen in Fig. 5(a),  $\Lambda$  is unable to follow the input signal at high frequencies. Fig. 5(b) reveals that the I-V loop shrinks as the frequency increases yielding a poor contrast between LSR and HRS. This is in agreement with what is expected from a memristive system [1].

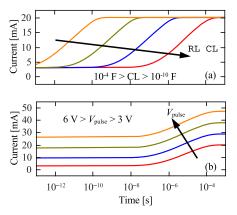

Next, the time evolution of the current under a constant voltage stimulus is analyzed. Fig. 6(a) shows the time evolution of the current as a function of the characteristic time  $\tau=\text{RL}$  CL. As expected, higher  $\tau$  values imply longer response times. The influence of the pulse amplitude  $V_{\text{pulse}}$  on the current evolution is shown in Fig. 6(b). It can be seen that the response time of the model is independent of the amplitude of the pulse. However, experiments exhibit an exponential relationship between switching time and applied voltage (see [25]). The model can be modified to include this effect if required. Taking into account the behavior shown in Fig. 6(a), (6) can be redefined as

$$\tau(V)\frac{\mathrm{d}\Lambda}{\mathrm{d}t} + \Lambda = \lambda(V) \tag{9}$$

Fig. 5. SPICE simulations showing the influence of input frequency on (a) evolution of the state variable  $\Lambda$  and (b) I-V characteristic curve. Cycles become more narrow with increasing frequency. The model parameters are the same as those in Fig. 3.

Fig. 6. SPICE simulations showing the dynamic behavior of the model. (a) Time evolution of the current as a function of  $\tau$ . (b) Influence of pulse amplitude on the time evolution of the current. The model parameters are the same as those in Fig. 3.

with

$$\tau(V) = \tau_0 \exp\left(-\frac{|V|}{v_0}\right) \tag{10}$$

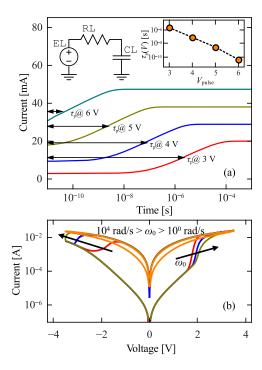

where  $\tau_0$  is the characteristic time in the absence of an applied signal and  $\nu_0$  parameterizes the switching rate. The functional relationship of (10) is based on experimental evidence [25], [26]. In order to solve (9), Block 3 must be changed according to the subcircuit shown in the inset of Fig. 7(a). Usually, there is no difference between the two ways of solving the differential equation but, as SPICE only allows resistors to depend on other variables, the latter approach is adequate to obtain the desired effect. The code modifications are shown in Table II. As it can be seen, the resistance exponentially depends on the applied voltage, as well the characteristic time  $\tau$ .

Fig. 7(a) shows the evolution of the current while applying constant voltage pulses of amplitude  $V_{\text{pulse}}$  and pulsewidth 1 ms. It can be seen that as  $V_{\text{pulse}}$  increases, the resulting transition time  $\tau_p$  decreases.  $\tau_p$  is defined as the time for which the current reaches the half value between its initial and final value. The inset of the figure shows  $\tau_p$  as a function

Fig. 7. Simulations regarding voltage-dependent characteristic time. (a) Influence of pulse amplitude on the current evolution. Inset: subcircuit proposed to solve (9) and  $\tau_p$  versus applied pulse amplitude. (b) I-V characteristic curve for different driving frequencies. The model parameters are the same as those in Fig. 3 except:  $\nu_0=0.3$  V and CL = 1 F.

#### TABLE II VOLTAGE-DEPENDENT CHARACTERISTIC TIME

```

** Block 3 - Current source - state variable **

* v0: switching rate parameter

.params v0=.3

BL 1 0 V=min(gm(V(PLUS,MINUS)),

+ max(gp(V(PLUS,MINUS)),V(L)))

R 1 L R=RL*exp(-abs(V(PLUS,MINUS))/v0)

C L 0 {CL}

.ic V(aux)=L0

```

of  $V_{\rm pulse}$ . Fig. 7(b) shows the I-V characteristic for different input signals. Notice that for higher frequencies the value of the switching threshold is also higher. Remarkably, within this approach, not only the collapse effect of the memristance is captured but also the variation of the effective switching threshold with the rate of change of the driving signal as reported in [26].

## C. Series and Parallel Configuration

In this section the model usefulness in circuit applications composed of more than one element is analyzed. This is motivated by the need to understand the functionality of memristive elements when they are combined in complex circuits. Two-element configurations are the simplest examples of these circuits. Here, anti-serial and anti-parallel connections of memdiodes are investigated.

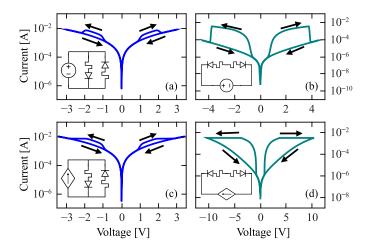

Fig. 8 shows the response of circuits comprising two identical memdiodes. In particular, Fig. 8(a) and (c) shows a combination of two memdiodes in an anti-parallel configuration while Fig. 8(b) and (d) presents results combining two memdiodes in an anti-series configuration. The simplicity of

Fig. 8. Hysteretic current-voltage characteristics for complementary resistive switches. (a) and (c) Anti-parallel memdiode circuit. (b) and (d) Anti-series memdiode circuit. Response of the circuit when applying a voltage input [(a) and (b)], and a current input [(c) and (d)]. Arrows indicate the direction of the cycle. Parameters are the same as those in Fig. 4.

the model allows to drive the circuit with a voltage source [Fig. 8(a) and (b)] or a current source [Fig. 8(c) and (d)]. This is of particular importance since very often experiments are conducted with any of these electrical sources.

The results for anti-series circuits are those expected for complementary resistive switching (CRS) devices in metal-oxide-metal structures [2], [27]. The model successfully reproduces the CRS operation and shows great versatility simulating circuits that involve various memristive elements driven by voltage or current sources. Interestingly, the response of the anti-parallel configuration is very similar to the CRS. The main difference is the voltage needed to reach the switching thresholds. The series configuration requires a larger amplitude because the voltage drop across each element depends on their resistive states. Regarding the circuit conductance, it can be observed that the series configuration provides the larger contrast between HRS and LRS.

# D. Model Validation

The model was put under test by fitting data extracted from different published works. In particular, Fig. 9(a) shows results obtained for a TaN/Al<sub>2</sub>O<sub>3</sub>/NbAlO/Al<sub>2</sub>O<sub>3</sub>/Pt structure at room temperature under DC voltage sweeps [28]. Fig. 9(b) presents results for a 5 nm-thick TiN/HfO<sub>2</sub>/Pt device [29]. The experimental data were fitted by (1) and (3) applying driving signals as described in the corresponding references. The fitted parameters are listed in the caption of Fig. 9. Note that the combination of signs of  $\eta^{\pm}$  and  $V^{\pm}$  determines the direction of rotation of the I-V loops, that is,  $\eta^{\pm}>0$  and  $V^{+}>V^{-}$  for counterclockwise rotation or  $\eta^{\pm}<0$  and  $V^{-}>V^{+}$  for clockwise rotation.

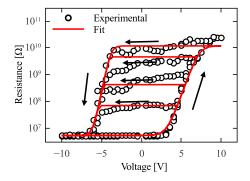

Finally, results regarding multilevel resistive states are shown in Fig. 10 where the pulsed write-voltage dependent resistance of an Au/DMO/NSTO/Au stack is illustrated [30]. In this case, the experimental data were fitted by (3) and the dynamic resistance dV/dI evaluated at 0.1 V as reported in the corresponding reference. As the switching between the

Fig. 9. Experimental I-V characteristics extracted from the literature. (a) TaN/Al<sub>2</sub>O<sub>3</sub>/NbAlO/Al<sub>2</sub>O<sub>3</sub>/Pt structure [28] and (b) TiN/HfO<sub>2</sub>/Pt device [29]. The fitted parameters are: (a)  $V^+=0.85$  V,  $V^-=-0.81$  V,  $\eta^+=277$  V $^{-1}$ ,  $\eta^-=346$  V $^{-1}$ ,  $I_0^{\rm min}=2\cdot 10^{-5}$  A,  $I_0^{\rm max}=1.25$  A,  $\alpha=2.24$  V $^{-1}$ ,  $R_S=87.5$   $\Omega$ , and Rmax =  $10^{10}$   $\Omega$  and (b)  $V^+=-0.55$  V,  $V^-=0.71$  V,  $\eta^+=-534$  V $^{-1}$ ,  $\eta^-=-24$  V $^{-1}$ ,  $I_0^{\rm min}=1.63\cdot 10^{-5}$  A,  $I_0^{\rm max}=8.23\cdot 10^{-3}$  A,  $\alpha=2.19$  V $^{-1}$ ,  $R_S=121$   $\Omega$ , and Rmax =  $10^{10}$   $\Omega$ .

Fig. 10. Experimental data extracted from [30]. The fitted parameters are:  $V^+=-6.09~\rm V, V^-=-3.19~\rm V, \eta^+=-3.37~\rm V^{-1}, \eta^-=-1.90~\rm V^{-1}, I_0^{min}=1.63\cdot 10^{-7}~\rm A, I_0^{max}=3.60\cdot 10^{-4}~\rm A, \alpha=0.50~\rm V^{-1}, R_{\it S}=1~\Omega,$  and Rmax =  $10^{10}~\Omega$ .

low and HRSs is smooth, intermediate resistive levels can be achieved by choosing the appropriate pulse amplitude.

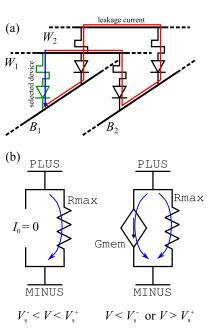

# E. Crossbar Array Elements

Usually, crossbar structures are comprised by a set of parallel bottom electrodes which are called bit-lines, a set of perpendicular top electrodes, called word-lines, and a given nonvolatile memory device which is located at the crossing points between these set of electrodes. The information can be stored by changing the state of each memory element. A typical structure is depicted in Fig. 11 where  $W_i$  stand for the word-lines and  $B_i$  for the bit-lines. Information is stored as follows: a positive voltage is applied to a particular junction via a pair of electrodes  $W_i$  and  $B_i$ , the resistive material turns to an LRS and remains in that state even in the absence of the external field. Similarly, the material is turned to an HRS if the applied voltage is negative. The information stored can be recalled by applying a voltage that is smaller than the writing thresholds and measuring the current flowing through the electrodes. Unfortunately, this simple reading procedure is not possible because the existence of parasitic currents arising

Fig. 11. (a) Crossbar array and leakage current problem. In the worst scenario, when all devices surrounding the selected device (green element) are in an LRS, the total current has both contribution from the addressed element (blue arrow) and its neighbors (red arrow). From the outside it is not possible to distinguish between these currents and it might lead to a wrong interpretation of the memdiode state. (b) Scheme of currents as a function of the applied voltage in the 1R1S structure.

from parallel elements. Fig. 11(a) exemplifies this problem in a  $2 \times 2$  crossbar array. This example shows the possibles pathways that the electrical current could take when the reading voltage is applied between electrodes  $W_1$  and  $B_1$ . The worst possible scenario is when all the elements are in an LRS and the desired element is in an HRS. In this case, the leakage current is not negligible in comparison to the addressed device, leading to a wrong interpretation of the stored state. One of the possible ways to overcome this problem is by means of a structure of the type 1R1S, that is, a resistive switching device in series with a selector device. The selector device imposes minimum voltage levels for electrical conduction. The main idea is that these thresholds are not reached by the parallel elements reducing the parasitic current in a considered way.

The 1R1S structure can be obtained by introducing a slight modification in the definition of  $\Omega$  in (8). Taking into account that the current is negligible when applying voltages lower than the thresholds of the selector, under this condition the memdiode must behave as a highly resistive device. This can be achieved by redefining  $\Omega$  as

$$\tilde{\Omega} = \Omega \left[ H \left( V - V_s^+ \right) + H \left( V_s^- - V \right) \right] \tag{11}$$

where  $V_s^{\pm}$  are the selector thresholds, and H(x) is the Heaviside function. The modification imposes that for voltages below the threshold levels the current amplitude factor must be  $I_0=0$ . In this way, the current through the device only flows across the resistance Rmax which is independent of the value of the internal state  $\Lambda$  as it is depicted in Fig. 11(b). Table III shows the model code that needs to be modified. Block 3.5 must be added since it accounts for the selector parameters and

#### TABLE III SELECTOR SPICE MODEL CODE

```

* Selector SPICE model

** Block 3.5 - Selector parameters **

* vps/vms: positive/negative selector threshold

.params vps=1.2 vms=-1

IO_s: modified current amplitude factor

* a s: modified alpha parameter

* Rs s: modified series resistance

.func sel(V) \{u(V-vps)+u(vms-V)\}

.func I0_s(L, V) \{I0(L) * sel(V)\}

.func a_s(V) {a*sel(V)}

.func Rs_s(V) {Rs*sel(V)}

** Block 4 - Current source - Selector **

Gmem PLUS MINUS value={sgn(V(PLUS,MINUS)) *

(1/(a_s(V(PLUS,MINUS)) *Rs_s(V(PLUS,MINUS))) *

w(a_s(V(PLUS,MINUS)) *Rs_s(V(PLUS,MINUS)) *

IO_s(V(L), V(PLUS, MINUS)) *exp(a_s(V(PLUS, MINUS)) *

(abs(V(PLUS, MINUS))+Rs_s(V(PLUS, MINUS)) *

I0_s(V(L),V(PLUS,MINUS)))))-I0_s(V(L),V(PLUS,MINUS)))}

Rmax PLUS MINUS {Rm}

```

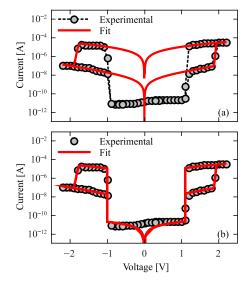

Fig. 12. Symbols stand for experimental data extracted from [31]. Solid red lines stand for fitted results. (a) Parameters are:  $V^+=1.94~\rm V$ ,  $V^-=-1.76~\rm V$ ,  $\eta^+=107\rm V^{-1}$ ,  $\eta^-=56~\rm V^{-1}$ ,  $I_0^{\rm min}=5.44\cdot 10^{-9}~\rm A$ ,  $I_0^{\rm max}=6.13\cdot 10^{-6}~\rm A$ ,  $\alpha=1.50~\rm V^{-1}$ ,  $R_s=25\cdot 10^3~\rm \Omega$ , and Rmax =  $5\cdot 10^{10}~\rm \Omega$ . (b) Selector thresholds are:  $V_s^+=1.2~\rm V$  and  $V_s^-=-1.0~\rm V$ .

defines the new parameters  $I_0$ ,  $\alpha$ , and  $R_s$  according to (11). Since the parameters given by (11) depend on the applied voltage, Block 4 needs to be modified.

Fig. 12 presents experimental data regarding an RRAM device integrated with an FAST selector [31]. Fig. 12(a) shows the fitted results of the RRAM device. In this case, data points that were above the selector thresholds were fitted by (1) and (3). Finally, in Fig. 12(b) the modification in  $\Omega$  is taken into account. Remarkably, numerical simulations considering (11) present a very good agreement with the experimental data, showing that the hysteron formalism is versatile to describe different structures and configurations.

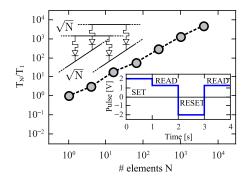

In order to study the convergence speed and accuracy, a large number of simulations were carried out. Fig. 13 shows the relative computation time  $T_N/T_1$  as a function of the crossbar array size shown in the inset of Fig. 13. The relative time was defined as the quotient between the simulation time of a system of N elements and the simulation time of a system of 1 element. The applied signal is shown in the inset of Fig. 13.

Fig. 13. Relative computation time as a function the crossbar size N.  $T_1 \approx 80$  ms. Inset: crossbar array under test and driving signal. The parameters are:  $V^+ = 2$  V,  $V^- = -1.8$  V,  $\eta^+ = 5$  V $^{-1}$ ,  $\eta^- = 5$  V $^{-1}$ ,  $I_0^{\min} = 10^{-5}$  A,  $I_0^{\max} = 10^{-3}$  A,  $\alpha = 1$  V $^{-1}$ ,  $R_s = 10$   $\Omega$ , and Rmax =  $10^{10}$   $\Omega$ . The selector thresholds are:  $V_s^+ = 1.2$  V and  $V_s^- = -1.0$  V.

It comprises an SET pulse of amplitude +2.0 V, a -2.0 V RESET pulse, and the corresponding READ pulses whose amplitudes are 1.25 V. It was found that the relative time increases exponentially with system size within the considered sizes. Many memristor SPICE models produce convergence errors during crossbar simulation, in particular, when the models were set to switch at a high frequencies signals [32]. Here, it was demonstrated that the proposed model not only can deal with large structures and include the selector device but it is also versatile and can fit a wide variety of devices.

# V. CONCLUSION

In this paper, an SPICE implementation of a novel compact model for nonlinear memristive devices was presented. A large number of simulations were conferred to elucidate the role of the parameters. The model showed to be stable under different input sources and amplitudes. Moreover, results regarding multielement circuits are a good evidence of the robustness of the model proposed where the CRS operation was successfully reproduced. The original model was modified in order to account for the frequency effect on the hysteresis loops and the transition time dependence with the applied voltage. Finally, the proposed model was validated with several experimental curves extracted from the literature. In this regard, the model was able to reproduce the multilevel resistive behavior as a consequence of the nature of the logistic hysteron formalism. In addition, by means of a slight modification, the model can also describe the behavior of 1R1S structures which are the cornerstone in the design of crossbar memory applications.

#### REFERENCES

- [1] L. O. Chua and S. M. Kang, "Memristive devices and systems," *Proc. IEEE*, vol. 64, no. 2, pp. 209–223, Feb. 1976.

- [2] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," Nat. Mater., vol. 6, no. 11, pp. 833–840, 2007.

- [3] M. Itoh and L. O. Chua, "Memristor oscillators," Int. J. Bifurcation Chaos, vol. 18, no. 11, pp. 3183–3206, 2008.

- [4] A. Sawa, "Resistive switching in transition metal oxides," *Mater. Today*, vol. 11, no. 6, pp. 28–36, 2008.

- [5] G. S. Snider, "Spike-timing-dependent learning in memristive nanodevices," in *Proc. IEEE Int. Symp. Nanoscale Archit. (NANOARCH)*, Anaheim, CA, USA, Jun. 2008, pp. 85–92.

- [6] B. Muthuswamy, "Implementing memristor based chaotic circuits," Int. J. Bifurcation Chaos, vol. 20, no. 5, pp. 1335–1350, 2010.

- [7] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, no. 7191, pp. 80–83, 2008.

- [8] D. Batas and H. Fiedler, "A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling," *IEEE Trans. Nanotechnol.*, vol. 10, no. 2, pp. 250–255, Mar. 2011.

- [9] A. Rak and G. Cserey, "Macromodeling of the memristor in SPICE," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 29, no. 4, pp. 632–636, Apr. 2010.

- [10] Z. Biolek, D. Biolek, and V. Biolková, "SPICE model of memristor with nonlinear dopant drift," *Radioengineering*, vol. 18, no. 2, pp. 210–214, 2009

- [11] I. Vourkas, A. Batsos, and G. C. Sirakoulis, "SPICE modeling of non-linear memristive behavior," *Int. J. Circuit Theory Appl.*, vol. 43, no. 5, pp. 553–565, 2015.

- [12] J. Blasco, N. Ghenzi, J. Suñé, P. Levy, and E. Miranda, "Modeling of the hysteretic I-V characteristics of TiO<sub>2</sub>-based resistive switches using the generalized diode equation," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 390–392, Mar. 2014.

- [13] E. Miranda, "Compact model for the major and minor hysteretic I-V loops in nonlinear memristive devices," *IEEE Trans. Nanotechnol.*, vol. 14, no. 5, pp. 787–789, Sep. 2015.

- [14] P. Lorenzi, R. Rao, F. Irrera, J. Suñé, and E. Miranda, "A thorough investigation of the progressive reset dynamics in HfO<sub>2</sub>-based resistive switching structures," *Appl. Phys. Lett.*, vol. 107, no. 11, 2015, Art. no. 113507.

- [15] E. Miranda, B. Hudec, J. Suñé, and K. Fröhlich, "Model for the current-voltage characteristic of resistive switches based on recursive hysteretic operators," *IEEE Electron Device Lett.*, vol. 36, no. 9, pp. 944–946, Sep. 2015.

- [16] M. A. Krasnosel'Skii and A. V. Pokrovskii, Systems With Hysteresis, 1st ed. Berlin, Germany: Springer-Verlag, 1989.

- [17] A. Ortiz-Conde, F. J. G. Sánchez, and J. Muci, "Exact analytical solutions of the forward non-ideal diode equation with series and shunt parasitic resistances," *Solid State Electron.*, vol. 44, no. 10, pp. 1861–1864, 2000.

- [18] S. Winitzki, "Uniform approximations for transcendental functions," in *Computational Science and Its Applications—ICCSA 2003* (LNCS 2667), V. Kumar, M. L. Gavrilova, C. J. K. Tan, and P. L'Ecuyer, Eds. Berlin, Germany: Springer, 2003, pp. 780–789.

- [19] P. Stoliar, M. J. Sánchez, G. A. Patterson, and P. I. Fierens, "Thermal effects on the switching kinetics of silver/manganite memristive systems," J. Phys. D Appl. Phys., vol. 47, no. 43, 2014, Art. no. 435304.

- [20] G. A. Patterson, F. S. Jimka, P. I. Fierens, and D. F. Grosz, "Memristors under the influence of noise and temperature," *Phys. Status Solidi C*, vol. 12, nos. 1–2, pp. 187–191, 2015.

- [21] C. Acha, "Electric pulse-induced resistive switching in ceramic YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7-δ</sub>/Au interfaces," *Phys. B Condensed Matter*, vol. 404, no. 18, pp. 2746–2748, 2009.

- [22] C. Walczyk et al., "Impact of temperature on the resistive switching behavior of embedded HfO<sub>2</sub>-based RRAM devices," *IEEE Trans. Electron Devices*, vol. 58, no. 9, pp. 3124–3131, Sep. 2011.

- [23] H. Abunahla, B. Mohammad, and D. A. Homouz, "Effect of device, size, activation energy, temperature, and frequency on memristor switching time," in *Proc. 26th Int. Conf. Microelectron. (ICM)*, Doha, Qatar, Dec. 2014, pp. 60–63.

- [24] M. Engelhardt, LTSpice/SwitcherCAD IV, Linear Technol. Corporat., Milpitas, CA, USA, 2011.

- [25] S. Gaba, P. Sheridan, J. Zhou, S. Choi, and W. Lu, "Stochastic memristive devices for computing and neuromorphic applications," *Nanoscale*, vol. 5, no. 13, pp. 5872–5878, 2013.

- [26] A. Rodriguez-Fernandez, C. Cagli, L. Perniola, J. Suñé, and E. Miranda, "Effect of the voltage ramp rate on the set and reset voltages of ReRAM devices," *Microelectron. Eng.*, vol. 178, pp. 61–65, Jun. 2017.

- [27] M. J. Rozenberg et al., "Mechanism for bipolar resistive switching in transition-metal oxides," Phys. Rev. B, Condens. Matter, vol. 81, no. 11, Mar. 2010, Art. no. 115101.

- [28] L. Chen et al., "Highly uniform bipolar resistive switching with Al<sub>2</sub>O<sub>3</sub> buffer layer in robust NbAlO-based RRAM," IEEE Electron Device Lett., vol. 31, no. 4, pp. 356–358, Apr. 2010.

- [29] L. Goux et al., "On the gradual unipolar and bipolar resistive switching of TiN/HfO<sub>2</sub>/Pt memory systems," Electrochem. Solid State Lett., vol. 13, no. 6, pp. G54–G56, 2010.

- [30] Z. Yan and J.-M. Liu, "Coexistence of high performance resistance and capacitance memory based on multilayered metal-oxide structures," *Sci. Rep.*, vol. 3, Aug. 2013, Art. no. 2482.

- [31] S. H. Jo, T. Kumar, S. Narayanan, W. D. Lu, and H. Nazarian, "3D-stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector," in *Proc. IEEE Int. Electron Devices Meeting*, San Francisco, CA, USA, Dec. 2014, pp. 6.7.1–6.7.4.

- [32] C. Yakopcic, T. M. Taha, G. Subramanyam, and R. E. Pino, "Memristor SPICE model and crossbar simulation based on devices with nanosecond switching time," in *Proc. Int. Joint Conf. Neural Netw. (IJCNN)*, Dallas, TX, USA, Aug. 2013, pp. 1–7.